**Carnegie Mellon University** Electrical & Computer Engineering

#### Obfuscation and Security for Digital Integrated Systems

Joe Sweeney, Larry Pileggi

| input<br>input<br>output<br>output<br>skg | <pre>128 (clk, start, state, key, out, out_valid);</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| k961                                      | NV0, KLD, KLD, KJD, KVD, KJD, KVD, KVD,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| start<br>end<br>wire st                   | rt_r:<br>@fpomedpe clk) begin<br>_r <= start;<br>art_pomedpe = start 4 ~start_r;<br>0] willdCounter;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| if(st<br>s0<br>k0<br>val<br>end<br>else   | <pre># (posedge cik) begin art_posedge begin art_posedge begin every every every every ideounter every ideount</pre> |

| assign                                    | out_valid = (validCounter == 0)/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

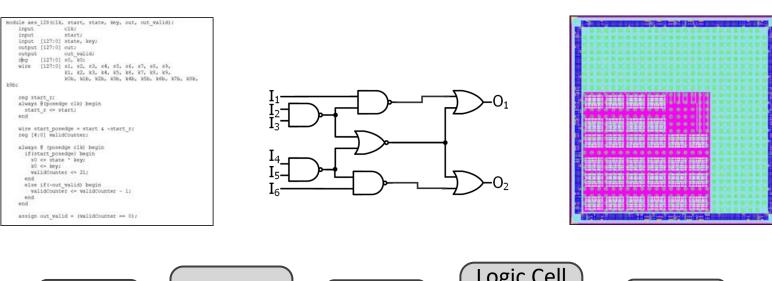

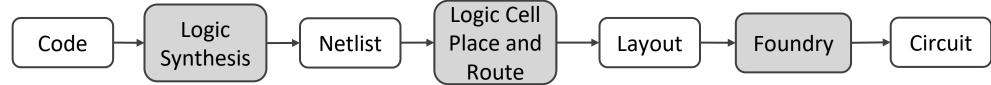

Code

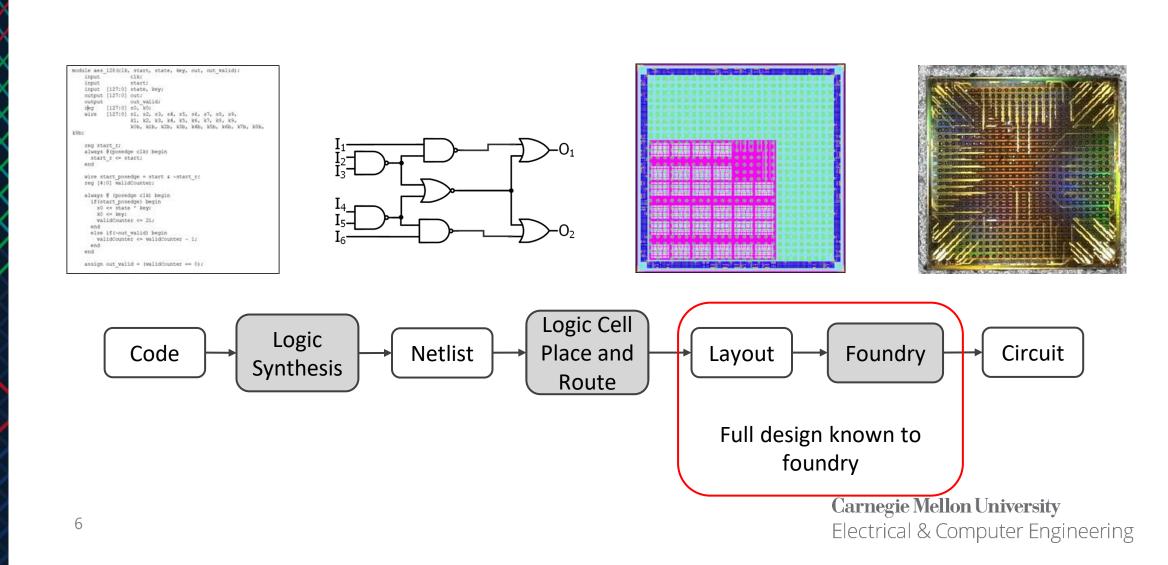

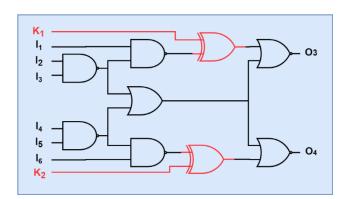

## Logic Locking Prevents Unauthorized Use

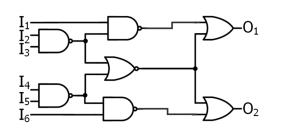

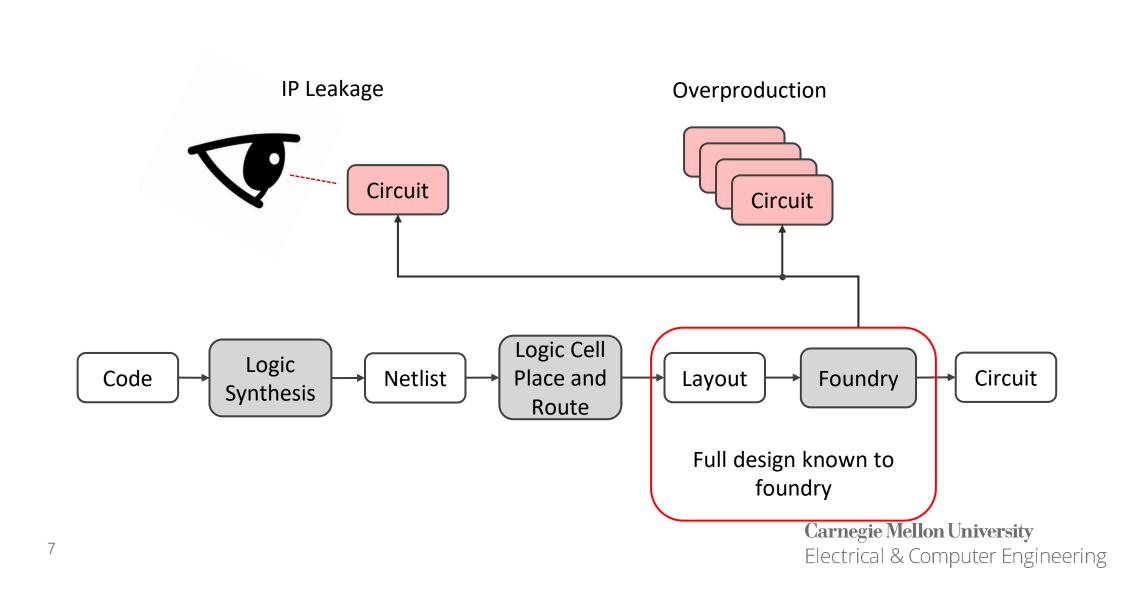

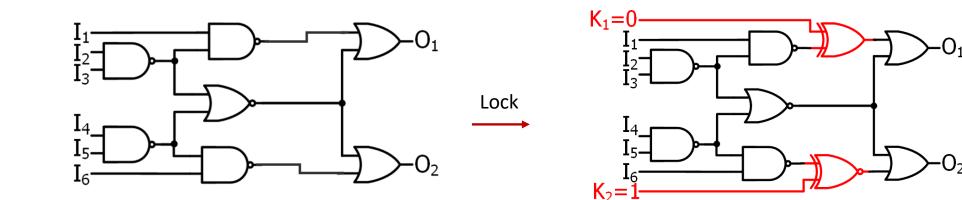

Logic locking adds programmable key elements to circuit

## Logic Locking Prevents Unauthorized Use

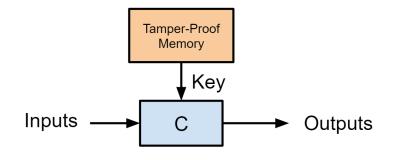

#### Manufacture locked circuit

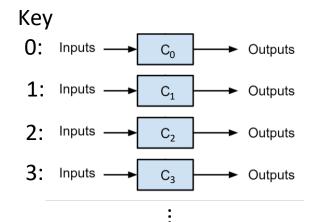

## Each key creates different functionality

Restore correct functionality with key stored in memory

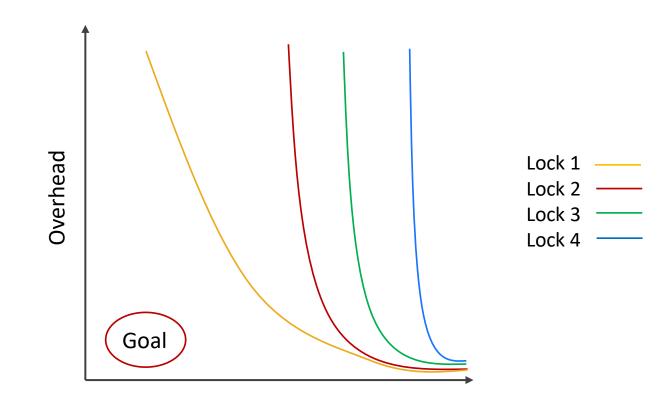

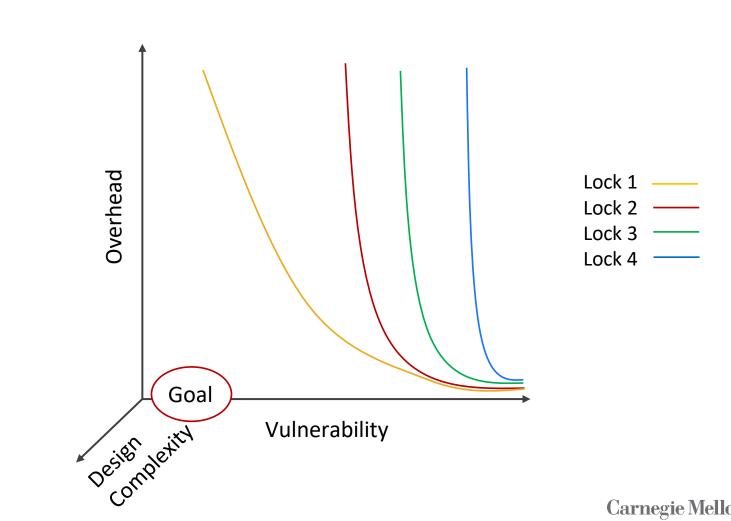

## Tradeoff of Logic Locking

Vulnerability

## Tradeoff of Logic Locking

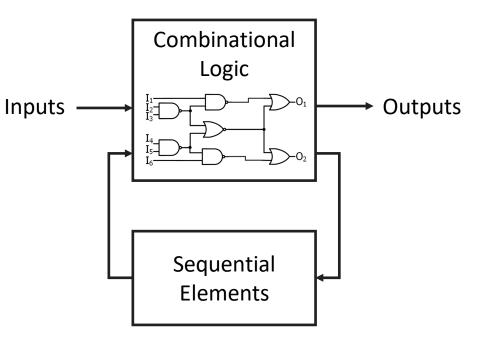

## Lock Sequential Elements

- Circuits made of combinational and sequential elements (memory)

- Current locking schemes target combinational logic

- Our technique manipulates the sequential elements

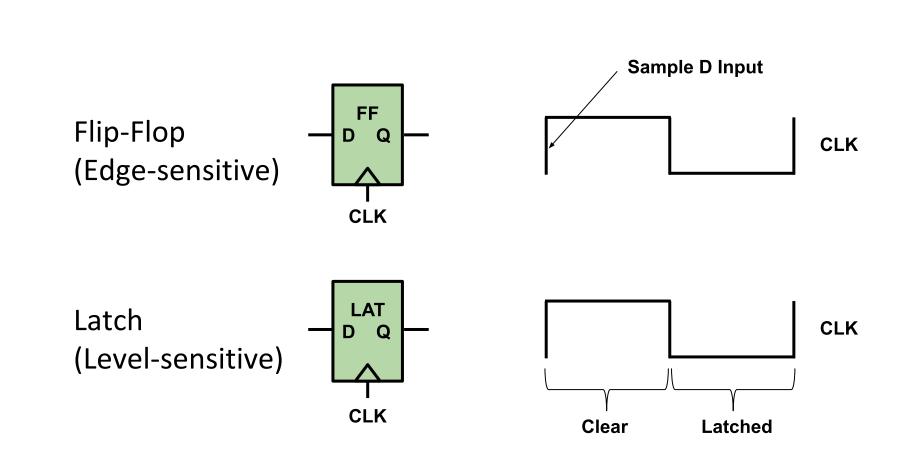

## Sequential Element Functionality

# Latch-Based Logic Locking (LBLL)

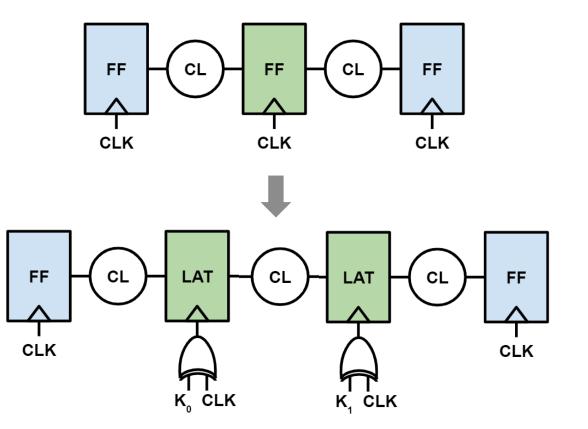

- Flip-flop can be broken into latches

- Allows flexible signal arrival times with cycle stealing

- Latch-based logic commonly used in high-speed design

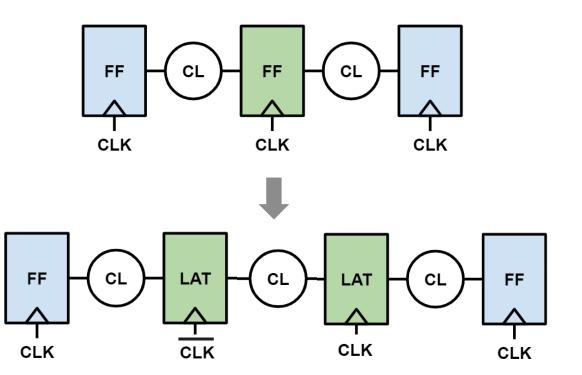

# Latch-Based Logic Locking (LBLL)

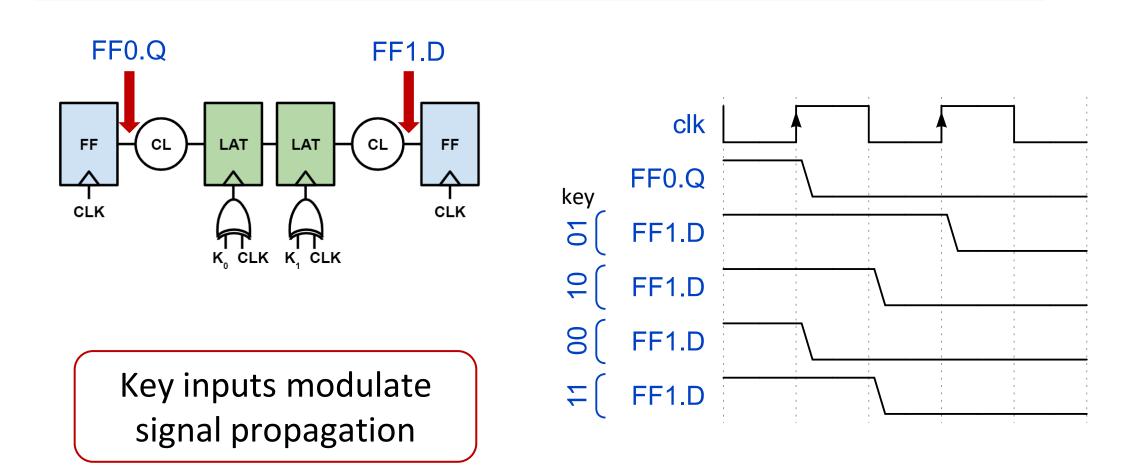

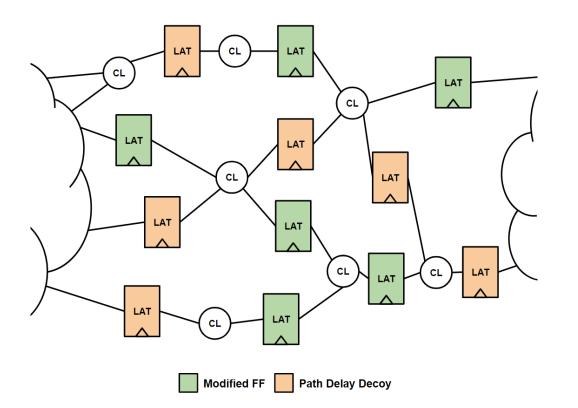

- LBLL repurposes this design style

- LBLL keys the latch clock phase for obfuscation

- Circuit manipulation not in critical path

## LBLL Programmable Path Delay

## LBLL Conceptual Diagram

- Portion of original flops converted to latches

- Delay decoys are held clear with correct key

- Resistant to all known attacks

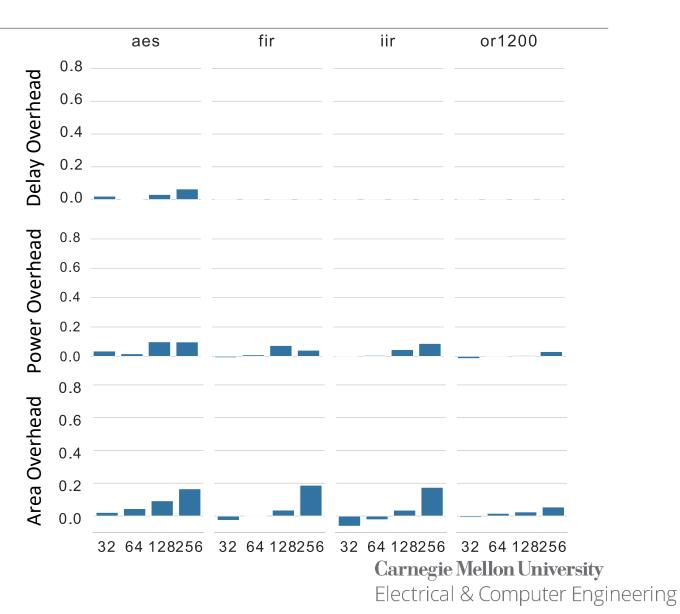

## Performance, Power, Area Overhead

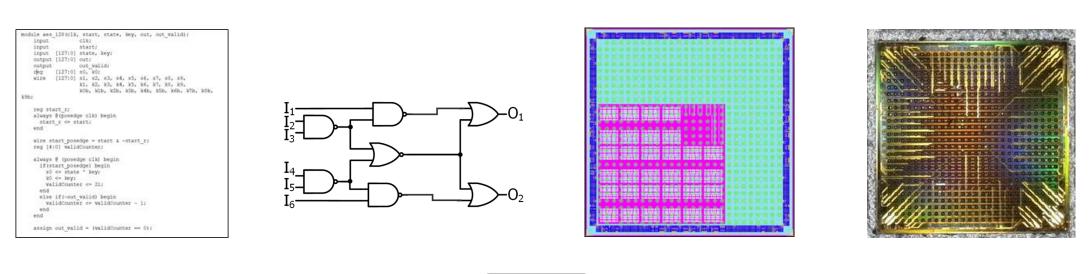

- Manufactured circuits in modern technology (22nm)

- Negligible delay overhead

- Small power and area increase

Top Level

18

## Summary

- Logic locking protects a design during manufacture

- Techniques must balance overhead with vulnerability

- LBLL provides a low overhead locking solution

# Thanks!